Binary Counters

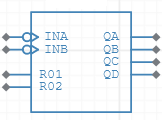

74LS93N Counter

74LS93N is a 4-bit binary counter that contains four master-slave JK flip-flops to provide a divide-by-eight counter, triggered by a HIGH-to-LOW transition of the clock input.

The count will be increased by 1 for

every pulse given to the clock pins INA and INB. The output bit QA is controlled

by INA and output bits QB,QC and QD are controlled by INB. To use all four bits the clock pulse INB must be connected to QA.

| Reset Inputs | Outputs | ||||

|---|---|---|---|---|---|

| R01 | R02 | QD | QC | QB | QA |

| H | H | L | L | L | L |

| L | X | COUNT | |||

| X | L | COUNT | |||

H = HIGH Level

L = LOW Level

X = Don't Care

| COUNT | Outputs | |||

|---|---|---|---|---|

| QD | QC | QB | QA | |

| 0 | L |

L |

L | L |

| 1 | L |

L |

L | H |

| 2 | L |

L |

H |

L |

| 3 | L |

L |

H |

H |

| 4 | L |

H |

L | L |

| 5 | L |

H |

L |

H |

| 6 | L |

H |

H |

L |

| 7 | L |

H |

H |

H |

| 8 | H | L |

L |

L |

| 9 | H | L |

L |

H |

| 10 | H | L |

H |

L |

| 11 | H | L |

H |

H |

| 12 | H | H | L | L |

| 13 | H | H | L |

H |

| 14 | H | H | H |

L |

| 15 | H | H | H |

H |

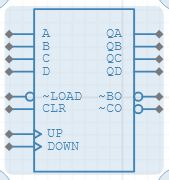

74LS193N Counter

74LS193N is a synchronous up/down 4-bit binary counter with dual clock.

Synchronous operation is provided by having all flip-flops clocked simultaneously, so that the outputs change together when so instructed by the steering logic.

The outputs of the four master-slave flip-flops are triggered by a LOW-to-HIGH level transition of either clock input. The direction of counting is determined by which clock input is pulsed while the other clock input is held HIGH.

The counter is fully programmable; that is, each output maybe preset to either level by entering the desired data at the inputs while the LOAD input is LOW.

The output will change independently of the clock pulses. This feature allows the counter to be used as a modulo-N divider by simply modifying the count length with the preset inputs. When CLEAR input is HIGH, it forces all outputs to the LOW level.

These counters were designed to be cascaded without the need for external circuitry. Both borrow (BO) and carry (CO) outputs are available to cascade both the up and down counting functions. The borrow output produces a pulse equal in width to the count down input when the counter under flows. Similarly, the carry output produces a pulse equal in width to the count up input when an overflow condition exists. The counters can then be easily cascaded by feeding the borrow and carry outputs to the count down and count up inputs respectively of the succeeding counter.

| CLR | ~LOAD | Up | Down | Mode |

|---|---|---|---|---|

| H | X | X | X | Reset(Async.) |

| L | L | X | X | Preset(Async.) |

| L | H | H | H | No Change |

| L | H | ↑ | H | Count Up |

| L | H | H | ↑ | Count Down |

H = HIGH Level

L = LOW Level

↑ = LOW-to-HIGH Clock transition

X = Don't Care